# Wafer-scale transistor arrays fabricated using slot-die printing of molybdenum disulfide and sodium-embedded alumina

대면적 슬롯 다이 프린팅을 활용한 이황화몰리브데늄 및 소듐 주입 알루미나 기반 트랜지스터 어레이

> Yonghyun Albert Kwon (Yonsei University) 권 용 현 (연세대학교)

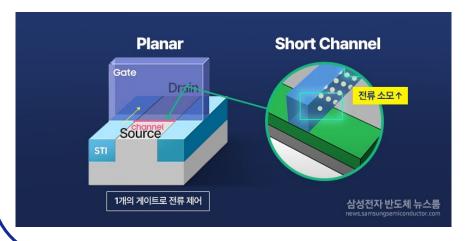

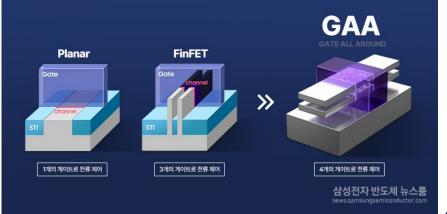

#### ◆ 반도체 소자의 미세화

- 반도체 칩의 집적도를 높이기 위한 미세화

- 1970년대 초반에 시작되어, 집적회로의 트랜지스터 밀도(집적도)를 지속적으로 높이면서 칩 크기를 축소

- 미세화가 진행됨에 따라 부작용(short channel effect;전류 제어에 있어 문제 발생)이 발생

- 현재는 이러한 부작용을 극복하기 위해 소자의 구조를 다변화함으로써 문제를 해결

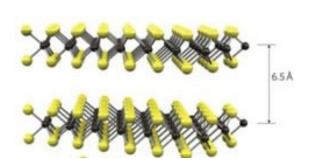

- 수 나노 이하 크기의 최첨단 소자를 구현하기 위해서는 <mark>반도체 채널의 두께</mark> 또한 수 나노 수준으로 얇아져야 함

- ▶ 이차원 반도체의 등장

- 기존 실리콘(Si)기반 반도체의 한계와 이차원 반도체의 등장

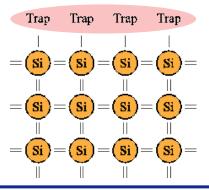

- 기존의 실리콘(Si) 반도체는 3차원 구조이기에 표면에 dangling bond (화학적 결합을 하지 않은 원자)가 존재하며 전자의 이동을 방해

- Si의 두께가 얇아질수록 dangling bond의 결함적 요소가 확대되어 성능이 급격히 저하됨 이차원 반도체는 원자 수준의 얇은 두께에서도 dangling bond가 존재하지 않아 미세화에 유리

- 이차원 반도체 중에서도 이황화몰리브데늄(MoS<sub>2</sub>)은 소재 내 전자 이동이 우수해 차세대 반도체로 주목됨

Si 반도체의 표면 결함

원자 수준 두께로 존재하는 MoS<sub>2</sub>

MoS, 이차원 반도체 소자

Nature Electronics, 5, 849-858 (2022)

- ♦ 이차원 반도체의 단점

- MoS2 반도체 소자의 상용화 걸림돌: 생산성과 성능

- 물리적 박리(mechanical exfoliation)를 통해 생산된 MoS₂는 높은 성능을 보이나 대면적 생산이 불가능

- 기상화학법(CVD)으로 생산된 MoS<sub>2</sub>는 전이(transfer)등의 추가 공정으로 인해 성능 저하

- 용액공정(solution process)으로 생찬된 MoS<sub>2</sub>는 대면적 생산이 가능하나 불순물 등의 영향으로 성능 저하

물리적 박리(mechanical exfoliation)

Sensors, 19(9), 2123 (2019)

#### 용액공정(solution process)

Nature, 562, 254-258 (2018)

#### 기상화학법(CVD)

Nature Electronics, 5, 275-280 (2022)

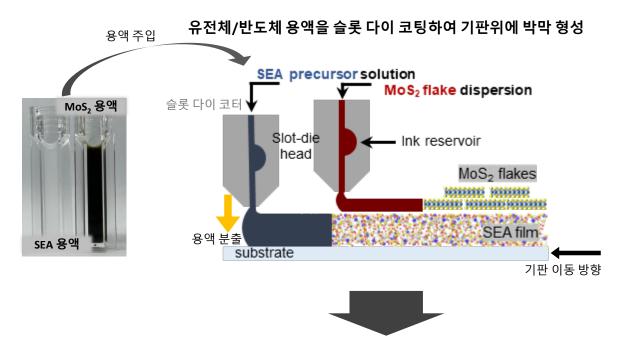

**SEA film**

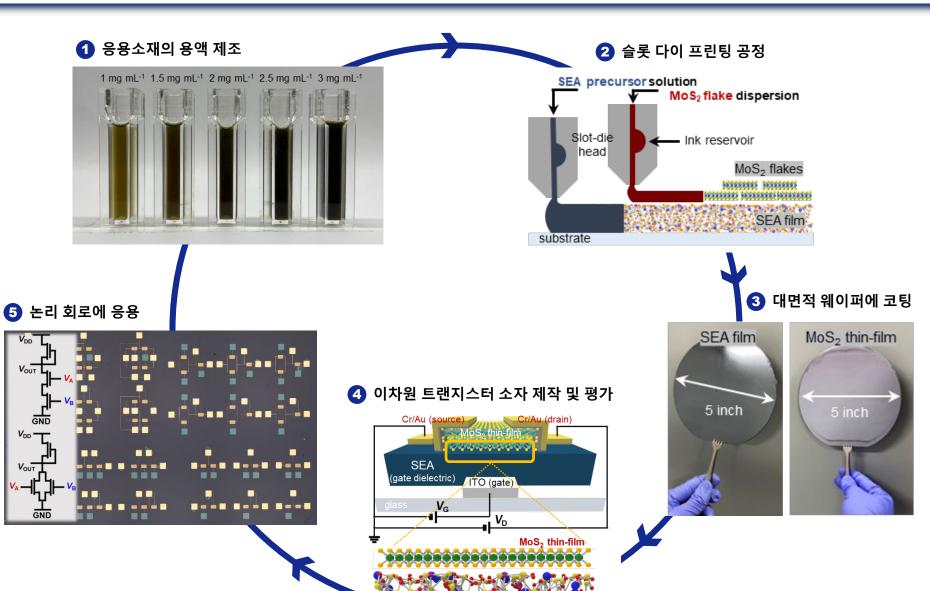

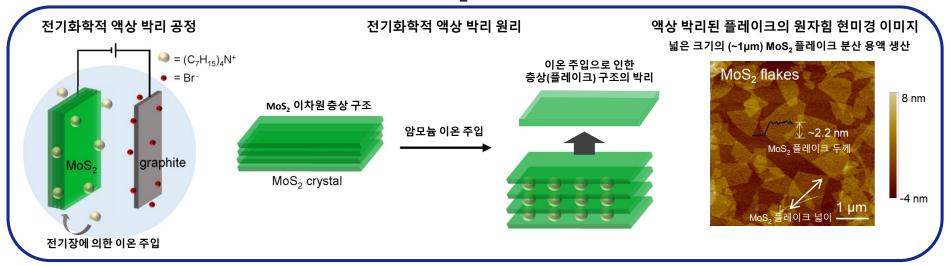

◆ 전기화학적 액상 박리 공정으로 MoS₂ 분산 용액 생산

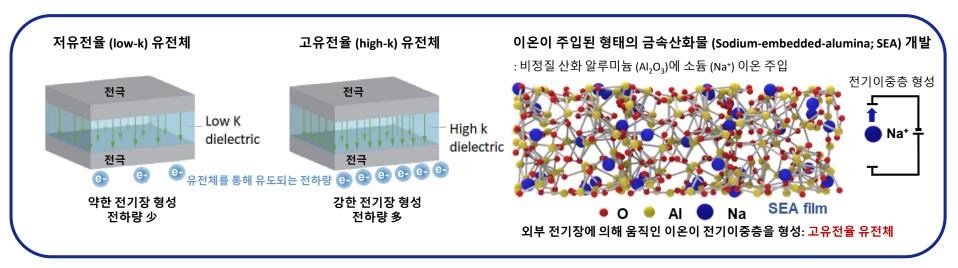

◆ 이온이 주입된 형태의 고유전율 금속산화물 유전체

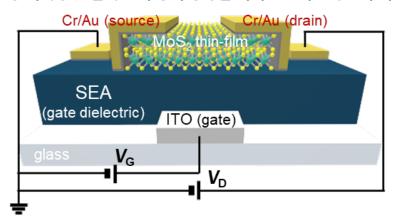

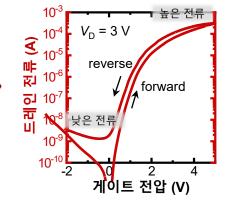

#### 트랜지스터 소자의 동작 : 전류 스위치

외부 전압(게이트 전압)에 따른 전류의 흐름이 변화

## 소자 최적화

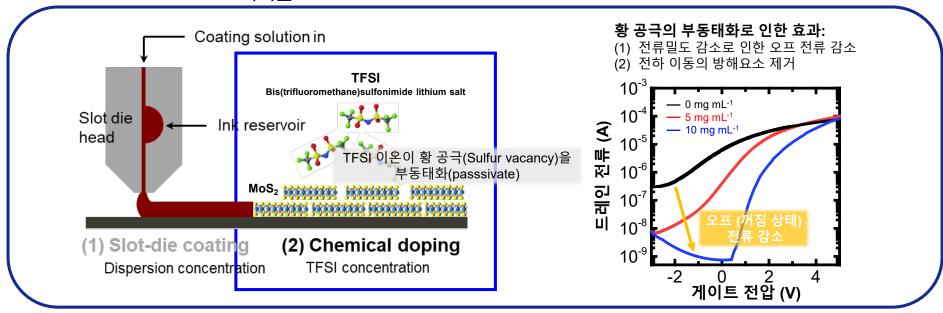

◆ 소자의 최적화 과정(1)\_화학적 도핑

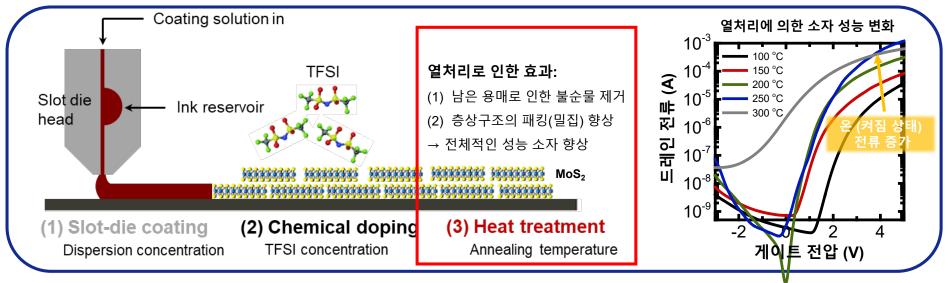

◆ 소자의 최적화 과정(2)\_열처리

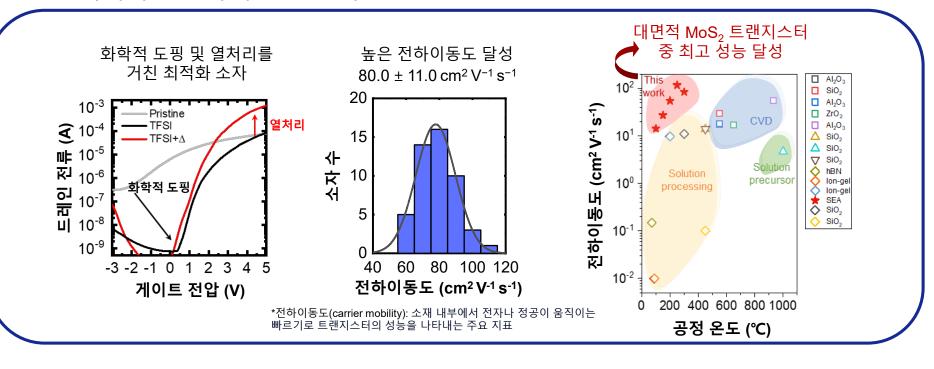

◆ 최적화된 소자의 성능 평가

### 소자 성능 분석

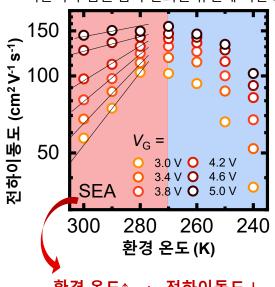

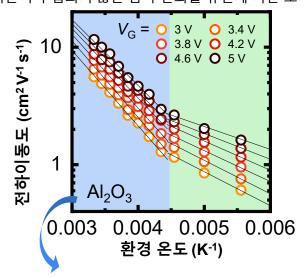

- ◆ 전하의 수송 메커니즘 분석

- 환경 온도에 따른 소자의 성능 변화를 통해 전하의 수송 메커니즘 분석

- 비교 분석을 위하여 이온이 주입되지 않은 산화 알루미늄 기반의 이차원 트랜지스터 측정

- 유전율 비교 : SEA > Al<sub>2</sub>O<sub>3</sub> (~ 17배)

#### MoS<sub>2</sub>/SEA 트랜지스터

이온이 주입된 금속 산화물 유전체 기반 소자

환경 온도↑ → 전하이동도↓

소재 내 결함이 없는 상태의 전하 이동 현상

MoS<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> 트랜지스터

이온이 주입되지 않은 금속 산화물 유전체 기반 소자

환경 온도↑ → 전하이동도↑

소재 내 결함이 존재하는 상태의 전하 이동 현상

높은 유전율로 인해 전하들이 소재 내 결함을 부동태화

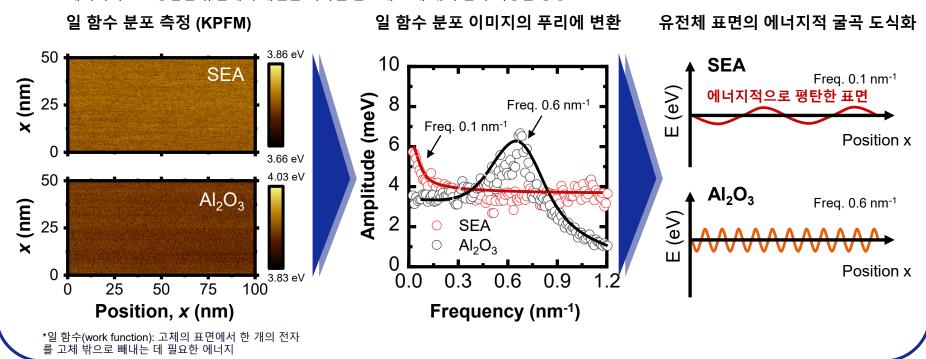

#### ◆ 유전 소재의 표면 분석

- KPFM(kelvin probe force microscopy)를 이용한 유전 소재의 표면 분석

- KPFM을 이용하여 소재의 일 함수(work function)\* 측정

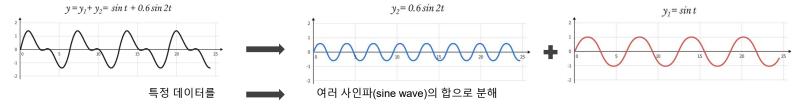

- 푸리에 변환 (Fourier transformation)\*\*을 통한 표면의 에너지적 굴곡을 분석

- 에너지적으로 평탄한 유전체의 계면은 이차원 반도체 소재 내의 전하 이동을 향상

\*\*푸리에 변환(Fourier transformation): 시간이나 공간에 대한 함수를 시간 또는 공간 주파수 성분으로 분해하는 변환

#### ◆ 논리 회로 응용

- 제작한 소자의 응용가능성 입증을 위해 논리 회로 구현

- 논리 회로 (Logic circuit) : 컴퓨터 연산을 수행하는 가장 기본 단위의 회로

- 논리 회로의 성공적인 구현을 통해 소자의 다양한 응용가능성을 증명

$V_{DD}$ : Inverter; 출력이 입력과 반대되는 값을 가짐 **NAND** Input voltage (V) : 모든 입력이 참일 **V**out 때에만 거짓 Output voltage (V)  $V_{\mathsf{DD}}$  $V_{\rm DD}$  = -2.0 V  $V_{\text{OUT}}$ -3.0 V  $V_{\mathsf{DD}}$ Output voltage (V) 2 NAND ACCURATE CONTROL OF THE PARTY O NOR : 모든 입력이 거짓 GND 일 때에만 참 Input voltage (V) Input voltage (V) NOR SRAM : Static random access memory; 전원이 공급되는 동안 데이터를 기억해주는 장치  $V_{\mathsf{DD}}$ V = open≥<sup>2</sup> 0  $V_{\text{IN}}$  $V_{\mathsf{OUT}}$ **5**<sup>2</sup> 80 20 40 60 100 120 140 160 GND Time (s)

# nature electronics

Explore content < About the journal < Publish with us <

nature > nature electronics > articles > article

Article Published: 08 June 2023

# Wafer-scale transistor arrays fabricated using slot-die printing of molybdenum disulfide and sodium-embedded alumina

Yonghyun Albert Kwon, Jihyun Kim, Sae Byeok Jo, Dong Gue Roe, Dongjoon Rhee, Younguk Song,

Byoungwoo Kang, Dohun Kim, Jeongmin Kim, Dae Woo Kim, Moon Sung Kang, Joohoon Kang

♣ Jeong

Ho Cho

Nature Electronics 6, 443–450 (2023) Cite this article

4555 Accesses | 38 Altmetric | Metrics

https://doi.org/10.1038/s41928-023-00971-7

\* 공동 교신 저자

조정호 교수

연세대학교

화공생명공학과

https://jhcho9400.wixsite.com/seplab

❖ 공동 교신 저자

강주훈 교수

성균관대학교

신소재공학부

https://sites.google.com/view/mfmp

❖ 공동 1저자 권용현 연구원 연세대학교 화공생명공학과

❖ 공동 1저자

김지현 연구원

성균관대학교

신소재공학부